# A New Large Signal HBT Model

Q. M. Zhang, Huntao Hu, John Sitch, R. K. Surridge, and Jimmy M. Xu

**Abstract**—Several effects important for large signal operations of heterojunction bipolar transistor (HBT's) were not included in the previous HBT models used in most commercial circuit simulators. Exclusion of these effects resulted in large discrepancies between modeled and measured device characteristics. This paper presents a new large signal HBT model which takes into account those important effects for the device operation. The effects have been identified from measured device characteristics and can be justified from first principles. To make it easy to use, the model is made up of the elements available from SPICE. During the course of the model development, an extraction procedure for the model parameters has been established to minimize the uncertainty of the extracted parameter values. The new model has been applied to HBT's with various emitter sizes and excellent agreement has been achieved between modeled and measured data over a wide range of bias conditions and signal frequencies.

## I. INTRODUCTION

**A**N ACCURATE device model valid for a wide range of operating biases and signal frequencies is required for the design of high-performance microwave circuits. Existing bipolar transistor models used in most commercial circuit simulators, which are based on the Gummel-Poon model [1], do not take into account several effects important for the prediction of large signal heterojunction bipolar transistor (HBT) performance. For example, the self-heating effect is omitted, which has been recognized as an important factor in determining HBT operations at high power dissipations. Efforts have been made to include this effect in HBT equivalent circuit models [2]–[4], and close agreements with measured data have been obtained for  $I_C - V_{CE}$  characteristics under constant  $I_B$  conditions. However, this does not ensure that the thermal models are correct under all conditions, for example, modeled  $I$ - $V$  characteristics under constant  $V_{BE}$  conditions are often not in agreement with measured values. Besides the self-heating, several other effects either have not been identified in the literature or not included in HBT equivalent circuit models. Omitting these effects from HBT models can result in large discrepancies between modeled and experimental data.

In this paper, we present a new HBT large signal model which takes into account several important effects for HBT operations. These are thermal effect, dependence of junction depletion capacitance and transit time on collector current, and variation of the effective electron barrier in an emitter heterojunction.

Manuscript received July 26, 1995; revised July 22, 1996.

Q. M. Zhang and J. M. Xu are with Nortel Technology, Ottawa, Canada and the University of Toronto, Canada.

H. Hu, J. Sitch, and R. K. Surridge are with Bell-Northern Research, Station C, Ottawa, Canada.

Publisher Item Identifier S 0018-9480(96)07902-1.

Our model was implemented in SPICE and all elements in the model are available in the simulator. Based on the understanding of the impacts of each model parameter on device characteristics, a procedure has been established to extract the parameters during the development of the model. The model was verified by the measured  $I$ - $V$  characteristics, junction capacitances and S-parameters over a wide range of bias conditions, as well as by power sweep measurement.

## II. MODEL

Behaviors of HBT's can be precisely described by a distributed network. The use of a lumped equivalent circuit to model HBT's is an approximation of the distributed network. Since the distributed network can be approximated in different ways, the resultant lumped equivalent circuits may have quite different configurations. Therefore, when constructing an equivalent circuit, one should take into account the device's physical structure, simplicity and accuracy of the circuit, and extractability of the circuit parameters. The selected circuit configuration for the large signal case should be also consistent with those for small signal and noise cases. Finally, it is preferable to have the equivalent circuit model implemented in a commercial circuit simulator.

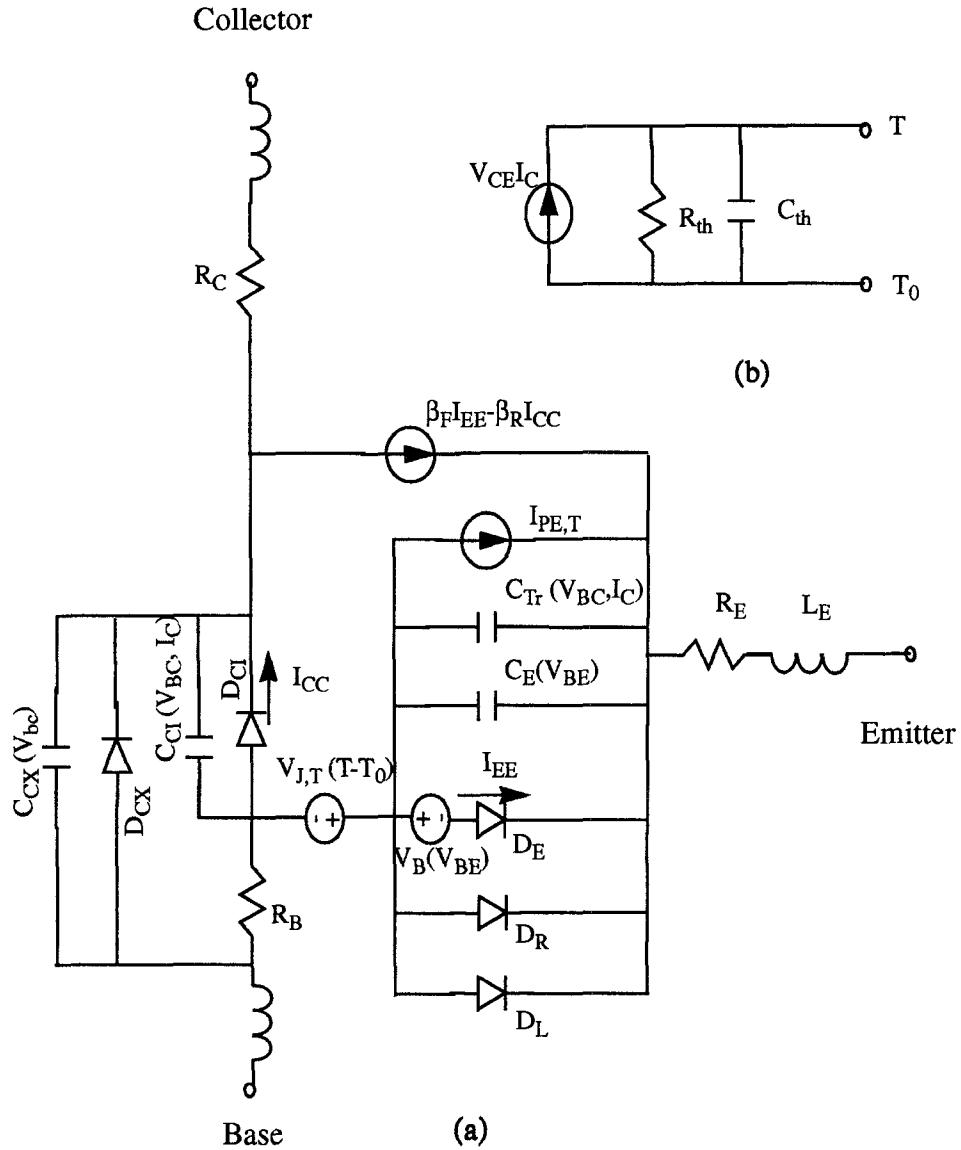

With the above guidelines in mind, the equivalent electric circuit as shown in Fig. 1 was constructed to develop the large signal model for HBT's. Also included in this figure is the thermal equivalent circuit, which is used to calculate temperature rise at the emitter junction. The configuration of the equivalent circuit is similar to that used for small signal model. Since the present goal is to develop a model for normal HBT operations, a breakdown mechanism is not included. The Kirk effect and substrate capacitance, which are believed to be unimportant for GaAs-based HBT's under normal operation conditions, are also ignored in this model.

### A. Bias-Independent Elements

Some parasitic elements of HBT's can be considered to be bias-independent. Such elements in the equivalent circuit are the series resistances of the emitter ( $R_E$ ), base ( $R_B$ ) and collector ( $R_C$ ), and the lead inductances of the emitter ( $L_E$ ), base ( $L_B$ ), and collector ( $L_C$ ).

### B. Diodes and Current-Controlled Current Source

Five diodes are used in the model to account for the currents flowing through the two p-n junctions and those caused by parasitic effects. In the circuit,  $D_E$ ,  $D_{CI}$ , and  $D_{CX}$  represent the emitter junction, and intrinsic and extrinsic collector junctions, respectively, while  $D_L$  and  $D_R$  model the

Fig. 1. Equivalent circuit topology of the large signal HBT model.

base-to-emitter leakage and the recombination at the device surface and in the emitter space-charge region. It is assumed here that all the currents represented by the diodes obey the Boltzman relation

$$I_d = I_S \left( \exp\left(\frac{V}{NV_T}\right) - 1 \right) \quad (1)$$

where  $I_S$  is saturation current of a diode,  $N$  is ideality factor of diode current, and  $V_T$  is the thermal voltage at junction temperature  $T$  and defined as  $V_T = kT/q$ . The current-controlled current source  $I_{CE}$  in the model is calculated from

$$I_{CE} = \beta_F \cdot I_{EE} - \beta_R \cdot I_{CC} \quad (2)$$

which is similar to that used in the Gummel-Poon model. In this equation,  $\beta_F$  and  $\beta_R$  are the forward and reverse current gains determined by the forward and reverse base transport factors, respectively.  $I_{EE}$  and  $I_{CC}$  are as defined in Fig. 1.

### C. Thermal Effects

Due to the large thermal resistivity of GaAs, thermal effects including self-heating are very important in GaAs-based HBT's and must be considered when determining the large signal performance of the device. With the thermal equivalent circuit given in Fig. 1(b), the temperature rise at the emitter junction can be calculated. The emitter junction temperature instead of the device temperature is used because the temperature distribution is nonuniform across the device and the most significant impacts of temperature rise on device performance occur at the emitter junction. The  $R_{th}$  in the circuit is the equivalent thermal resistance corresponding to the junction temperature rise. For simplicity, a constant value is used here for  $R_{th}$ . However, its temperature dependence can be readily incorporated into the model.

Two major consequences from the temperature rise in AlGaAs/GaAs HBT's are the decrease in the emitter junction built-in potential and the increase in the reverse hole injection

from the base to emitter. The former is responsible for the increase in the collector current under constant  $V_{BE}$  conditions, and the latter causes the decrease in the collector current under constant  $I_B$  conditions as  $V_{CE}$  increases. Both are identifiable from device measurements.

Under constant  $V_{BE}$  conditions, the emitter current as a function of the junction temperature may be approximated as

$$I_E = I_{SO} \cdot \left( \exp\left(\frac{1}{NV_{TO}}(V_{BE} + V_{J,T})\right) - 1 \right). \quad (3)$$

In the above equation,  $I_{SO}$  and  $V_{TO}$  are saturation current and thermal voltage at ambient temperature  $T_o$ , respectively. The exponential temperature dependence of saturation current  $I_S(T)$  is taken into account by  $V_{J,T}$ , which is the reduction of the emitter junction built-in potential due to the temperature rise and can be expressed as

$$V_{J,T} = \left( \frac{\partial}{\partial T}(V_{BE}) \Big|_{I=const} \cdot (T - T_o) \right). \quad (4)$$

In a circuit model,  $V_{J,T}$  can be effectively modeled by using a temperature controlled voltage source defined by (4). The temperature coefficient of E-B junction was extracted from  $I-V$  characteristics of the E-B junction diode at different ambient temperatures. With this treatment, the junction diode temperature can be set at  $T_o$ , which is required by most circuit simulators.

Under constant  $I_B$  conditions, the decrease in the collector current with  $V_{CE}$  is caused by the drop of current gain  $\beta$  as the junction temperature increases. Since the temperature impact on the base transport factor of GaAs-based HBT's is not significant [5], the reduction in  $\beta$  is attributed to the reduced emitter efficiency. The emitter efficiency is solely determined by the injection ratio of holes ( $I_{PE}$ ) to electrons ( $I_{NE}$ )

$$\frac{I_{PE}}{I_{NE}} = \frac{D_E N_B W_B}{D_B (N_E \cdot W_E)} \cdot \exp\left(-\frac{\Delta E_V}{kT}\right). \quad (5)$$

In this equation,  $\Delta E_V$  is valence-band offset of an emitter heterojunction,  $D_E$  and  $D_B$  are hole diffusion coefficient in the emitter and electron diffusion coefficient in the base,  $N_B$  and  $N_E$  are base and emitter doping concentrations, and  $W_B$  and  $W_E$  are base and emitter layer thicknesses. It can be seen from (5) that the injection ratio has an exponential dependence on temperature due to the valence band offset of the heterojunction. By applying Taylor expansion to (5) and considering  $I_{NE}(T) = I_{NE}(T_o) \cdot \exp(V_{J,T}/NV_{TO})$  from the equivalent circuit in Fig. 1, the increase in backward hole injection current (represented by  $I_{PE,T}$  in the model) is derived as

$$I_{PE,T} = I_{PE}(T) - I_{PE}(T_o) = I_{PE}(T_o) \sum_{n=1}^{\infty} \frac{1}{n!} x^n \quad (6)$$

with

$$x = \frac{V_{J,T}}{NV_{TO}} \frac{\Delta E_V}{kT_o} \frac{(T - T_o)}{T}. \quad (7)$$

This expression indicates that we can use a polynomial function of temperature rise to simulate the increase in the backward hold injection current.

#### D. Effective Electron Barrier Variation

In an abrupt emitter junction, a conduction band spike appears at the junction, which impedes the electron injection from the emitter to the base. Although the spike height, which is mainly determined by the conduction band offset of the heterojunction, is not bias dependent, the electron tunneling probability through the spike does vary with bias. This is equivalent to an effective barrier ( $\Delta E_C$ ) which changes with bias. The injection current including the barrier effect can be expressed by

$$I = I_S \cdot \left( \exp\left(\frac{V_{BE} - \Delta E_C(V_{BE})}{N_O V_T}\right) - 1 \right) \quad (8)$$

where  $N_O$  is the ideality factor without the barrier effect. The barrier  $\Delta E_C(V_{BE})$  is modeled by a voltage-controlled voltage source  $V_B(V_{BE})$  in the model (see Fig. 1). To derive the expression for  $V_B(V_{BE})$ , we use another expression of the injection current which reflects the fact that the ideality factor of collector current varies with bias due to the barrier variation

$$I = I_S \cdot \left( \exp\left(\frac{V_{BE}}{N(V_{BE}) V_T}\right) - 1 \right). \quad (9)$$

From (8) and (9), the relation between the  $V_B(V_{BE})$  and  $N(V_{BE})$  is derived as

$$V_B(V_{BE}) = V_{BE} N_O \left( \frac{1}{N_O} - \frac{1}{N(V_{BE})} \right). \quad (10)$$

This expression is used to construct  $V_B(V_{BE})$  in the model where  $N(V_{BE})$  is obtained from the measured  $I_C - V_{BE}$  curve.

In a graded emitter junction, the barrier is significantly reduced by composition grading. But it can not be completely removed. Therefore, the barrier exists to some extent in a graded emitter junction as well.

#### E. Capacitors

Capacitors are used to model the transit time and charge storage mechanisms in the large signal model. In the model (see Fig. 1),  $C_E$ ,  $C_{CI}$ , and  $C_{CX}$  represent the capacitances for the base-emitter, the intrinsic and extrinsic base-collector junctions, respectively. Based on the charge-control theory, transit time is lumped as a capacitor ( $C_{Tr}$ ) parallel to  $C_E$ .

The classic expression for a junction depletion capacitance assumes that either no current flows or carriers pass through the junction at infinite velocity. However this assumption may not be valid for both junctions of HBT's under normal operations. The electron concentration in the junction depletion regions, which supports the current flow, may be comparable with the donor density there, leading to charge compensation in the  $n$ -type depletion region. Due to the charge compensation, the  $n$ -type depletion region must be expanded to maintain the charge neutrality of the junction assuming that the total charge in the  $P^+$ -type depletion region is not changed. As a result, the depletion capacitance decreases with current until the electron concentration exceeds the donor density  $N_D$ . To account for this effect, the charge density  $qN_D$  in classical expressions of depletion capacitances [6] should be replaced by  $q(N_D - n)$ , where  $n$  is the average electron density in the depletion region.

By using the relationship between the current and  $n$ , a general expression for the capacitance calculation may be given by

$$C = C(V) \cdot (1 - (\eta_1 \cdot I))^{\eta_2} \quad (11)$$

where  $C(V)$  is the capacitance at the zero current, and  $\eta_1$  and  $\eta_2$  are parameters determined by the electron velocity, the junction area and the junction doping profile. This treatment was applied to the intrinsic collector depletion capacitance ( $C_{CI}$ ) in the model. The extrinsic collector ( $C_{CX}$ ) and the emitter ( $C_E$ ) depletion capacitances were treated classically (i.e., without considering their current dependence) since no significant current flows through the extrinsic collector junction and the emitter doping level is usually an order of magnitude higher than that of the collector.

The transit time capacitor  $C_{Tr}$  in the Gummel-Poon model is related to the total transit time  $\tau_{Tr}$  and transconductance  $g_m$  by

$$C_{Tr} = \frac{dQ_n}{dV_{be}} = \left( \frac{dQ_n}{dI_C} \right) \left( \frac{dI_C}{dV_{be}} \right) = \tau_{Tr} \cdot g_m \quad (12)$$

where  $Q_n$  is the total electron charges of a npn transistor. In the Gummel-Poon model, a constant value is used for  $\tau_{Tr}$ . In fact,  $\tau_{Tr}$  is a function of both  $V_{CB}$  and  $I_C$ . The  $V_{CB}$  dependence of the transit time mainly results from the change in the collector junction depletion width with  $V_{CB}$  and the  $I_C$  dependence is due to the variation of the electron velocity as  $I_C$  changes. Taking into account these effects, we can express  $C_{Tr}$  in a general form

$$C_{Tr} = \left( b_0 + b_1 \cdot \left( 1 + \frac{V_{CB}}{V_J} \right)^{b_2} \right) \cdot I_C^{b_3} \quad (13)$$

where  $V_J$  is the built-in potential of the collector junction and  $b_0 - b_3$  are the parameters determined by the device physical structure. In this equation

$$\left( b_0 + b_1 \cdot \left( 1 + \frac{V_{CB}}{V_J} \right)^{b_2} \right)$$

is the voltage-dependent term and  $I_C^{b_3}$  is the current-dependent one. If  $\tau_{Tr}$  is independent of current,  $b_3 = 1$  due to  $g_m \sim I_c$ . In this case,  $b_0$  is the base transit time and

$$\left( b_1 \cdot \left( 1 + \frac{V_{CB}}{V_J} \right)^{b_2} \right)$$

is collector transit time.

The above treatment on transit time only includes its effect on signal magnitude because it is found that the effect on signal magnitude is more important than that on signal phase. However, the effect on signal phase can be modeled by introducing a phase factor in the current-controlled current source of the equivalent circuit, as that used in Gummel-Poon model.

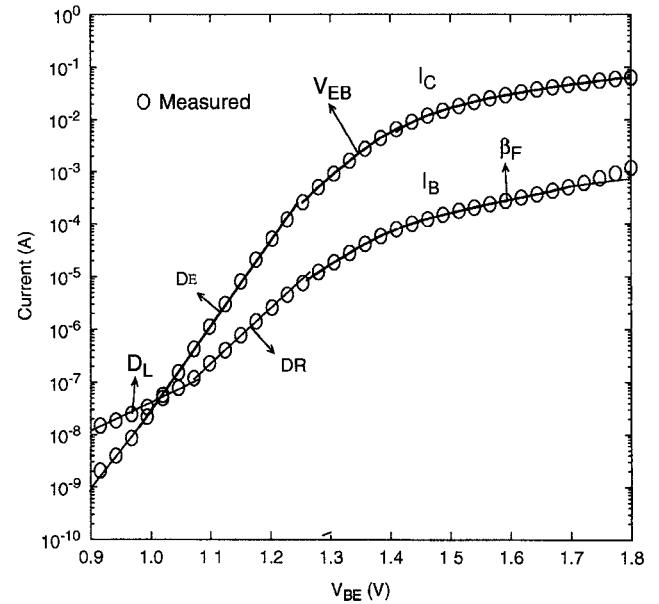

Fig. 2. Gummel plot of a BNR HBT with an abrupt emitter-base junction, showing the sections on the curves (lines) to extract the corresponding parameters.

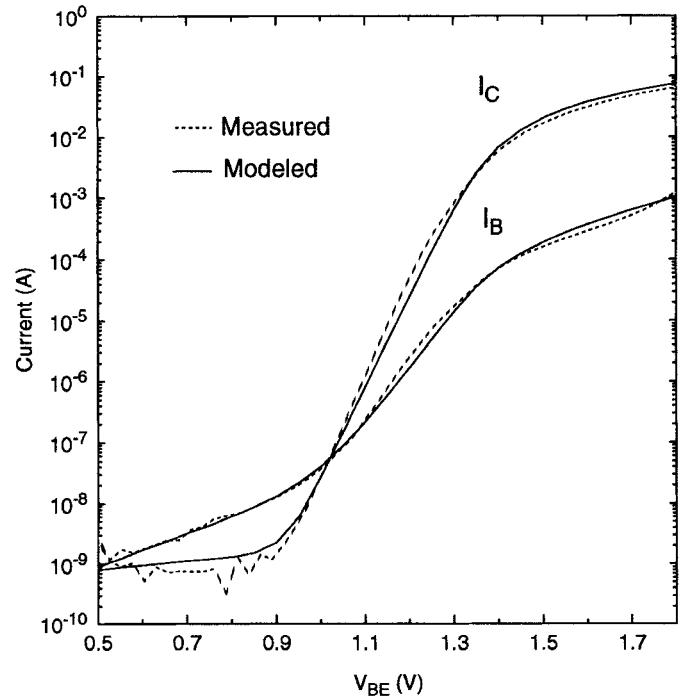

Fig. 3. Comparison of the modeled and measured Gummel plot for the HBT given in Fig. 4.

### III. PARAMETER EXTRACTION

To minimize the uncertainty of parameter extraction, it is necessary to use a complete set of the measurable device characteristics which contain the information about all the elements in the model. For this reason, the dc and small-signal microwave characteristics under several sets of representative bias conditions were measured and used to extract the parameters of the large signal HBT model in this work. During the development of the model, the effects of each element on the

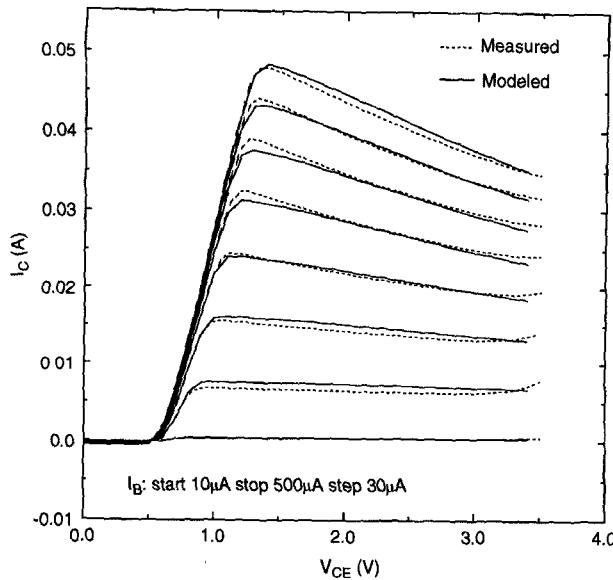

Fig. 4. Comparison of the modeled and measured  $I$ - $V$  characteristics under constant  $I_B$  conditions.

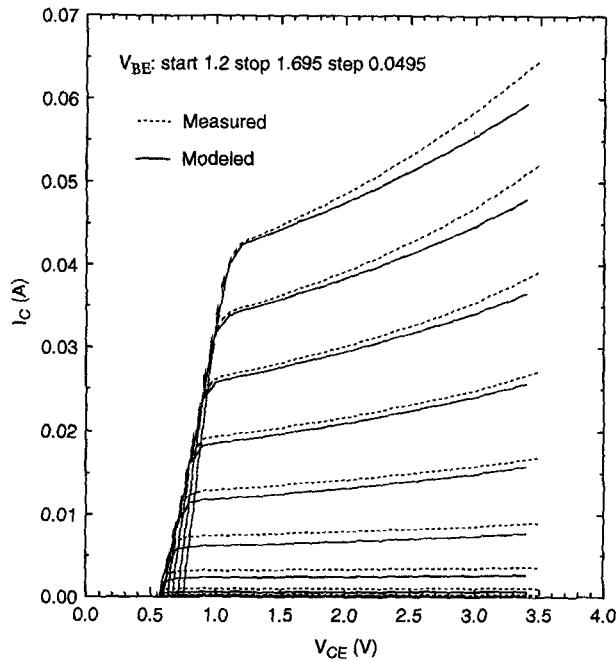

Fig. 5. Comparison of the modeled and measured  $I$ - $V$  characteristics under constant  $V_{BE}$  conditions.

device characteristics were studied and identified. Based on the understanding of these effects, the characteristics which are the most sensitive to certain elements were used to extract those element values.

#### A. Extraction for Bias-Independent Elements

In the developed extraction procedure, the bias independent element values were extracted from dc measurements and small-signal S-parameters. These elements include six parts.

- 1)  $R_E$ : measured by using the open collector method [7].

- 2)  $R_C$ : estimated from Z-parameters which was converted

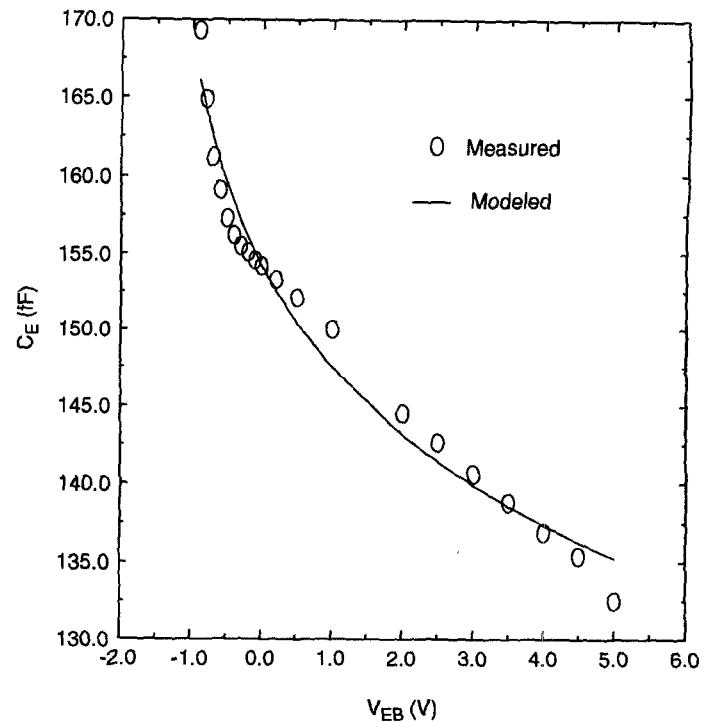

Fig. 6. Comparison of the modeled and measured base-emitter junction depletion capacitance.

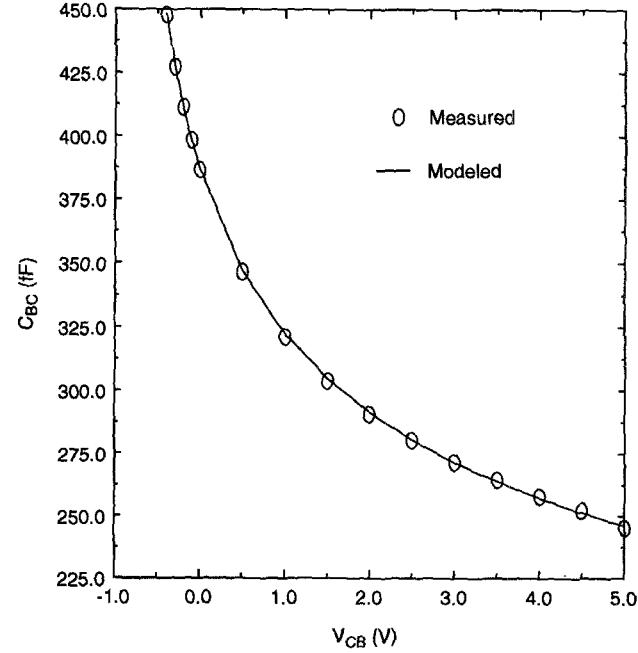

Fig. 7. Comparison of the modeled and measured total base-collector junction capacitance at  $I_C = 0$ .

from measured small signal S-parameters.

$$R_C = \{2\pi f[\text{Im}(Z_{21}) - \text{Im}(Z_{12})]\}^{-1}. \quad (14)$$

- 3)  $R_B$ : estimated from measured  $C_{bc}$ ,  $f_T$  and  $F_{\max}$

$$R_B = \frac{f_T}{8\pi C_{BC} f_{\max}^2}. \quad (15)$$

- 4)  $L_E$ ,  $L_B$ , and  $L_C$ : determined by using the optimization for the small signal model of HBT's.

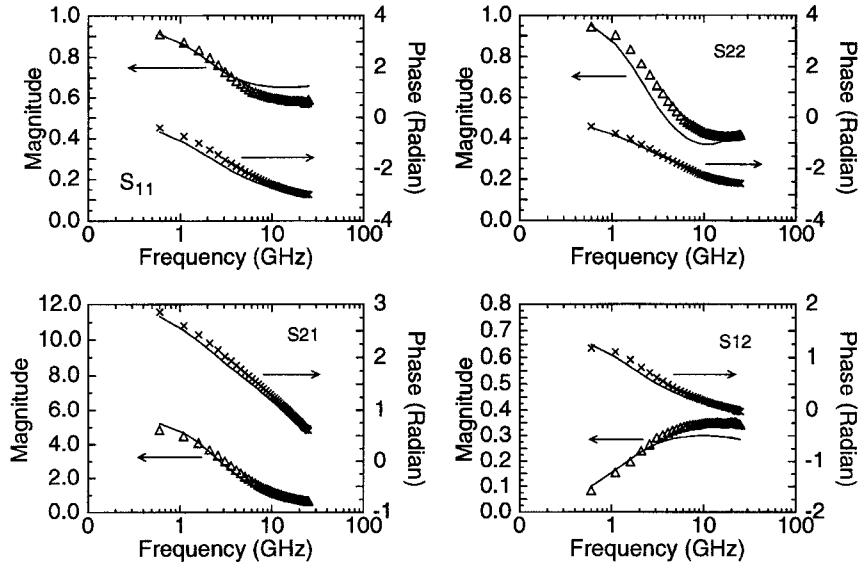

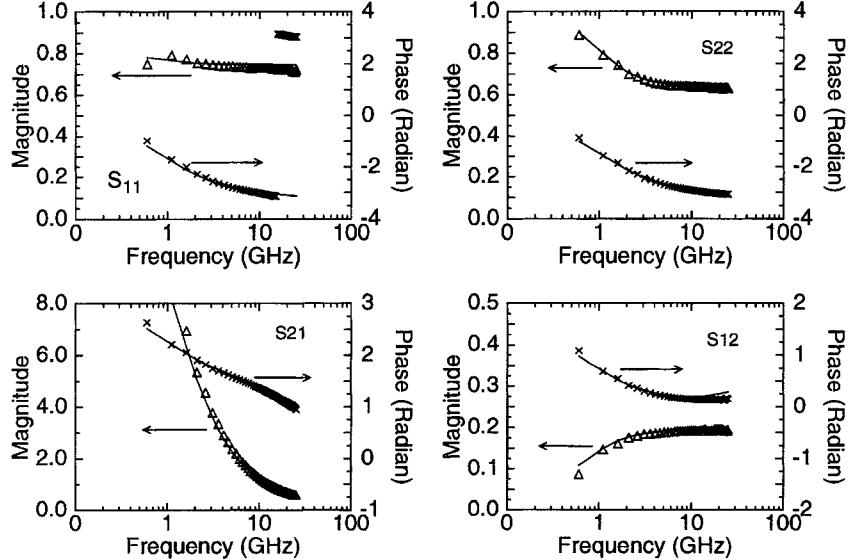

Fig. 8. Comparison of S-parameters from modeling (solid lines) and measurement (symbols) at bias condition of  $V_{BE} = 1.35$  and  $V_{CE} = 3.6$  V.

Fig. 9. Comparison of S-parameters from modeling (solid lines) and measurement (symbols) at bias condition of  $V_{BE} = 1.65$  V and  $V_{CE} = 1.65$  V.

- 5)  $\beta_F$ : determined from measured Gummel plot, as indicated in Fig. 2.

- 6)  $\beta_R$ : obtained from measured reverse-mode Gummel plot with the assumption that the maximum current gain is equal to  $\beta_R$ .

#### B. Bias Dependent Elements For DC Characteristics

The dc  $I$ - $V$  characteristics of the transistor are primarily determined by noncapacitive bias-dependent elements. These elements are the collection junction diodes  $D_{CI}$  and  $D_{CX}$ , the leakage diode  $D_L$ , the recombination diode  $D_R$ , the emitter junction diode  $D_E$ , and the controlled voltage source  $V_{EB}$  which accounts for the additional electron barrier at an abrupt emitter junction.

The parameters of  $D_{CI}$  and  $D_{CX}$  were extracted from the  $B$ - $C$  junction  $I$ - $V$  characteristics. The same ideality factors were assumed for the two diodes. The measured saturation

current was partitioned between  $D_{CI}$  and  $D_{CX}$  according to their area ratio. This allows the parameters of the two diodes to be extracted from one  $I$ - $V$  measurement.

The other bias-dependent parameters were extracted from different sections on the Gummel plot, as indicated in Fig. 2. Based on the analysis of the impacts of each element on the Gummel plot, the section which is most sensitive to an element was chosen to extract the parameters of the element. For example, the base current is dominated by leakage current at low  $V_{BE}$  and by recombination current in medium  $V_{BE}$  regime; therefore, these two sections on the  $I_B$ - $V_{BE}$  curve were used to obtain the parameters of  $D_L$  and  $D_R$ , respectively.

$D_L$  models the leakage current between emitter and base. The leakage current is featured by a very large ideality factor, which is much larger than 2. The cause for such a current has not been well understood yet. The recombination current which

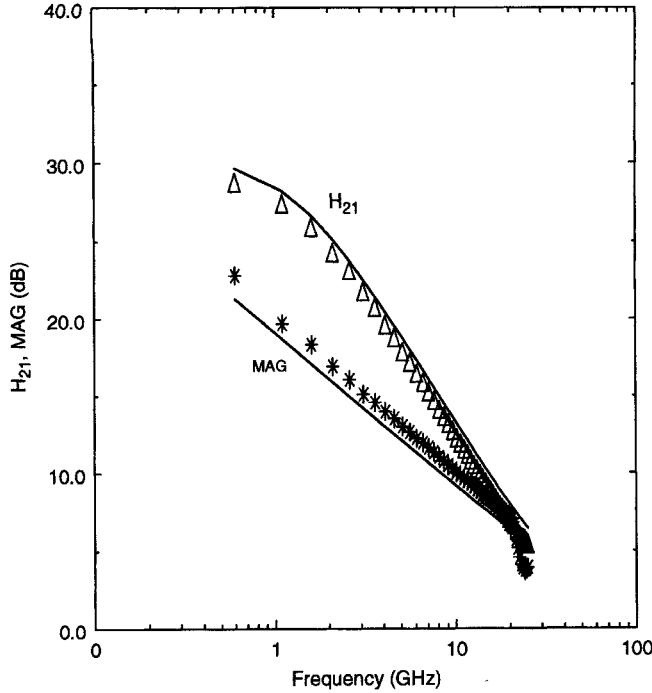

Fig. 10. Comparison of the modeled (solid lines) and measured (symbols) frequency response at  $V_{BE} = 1.4$  V and  $V_{CE} = 1.4$  V.

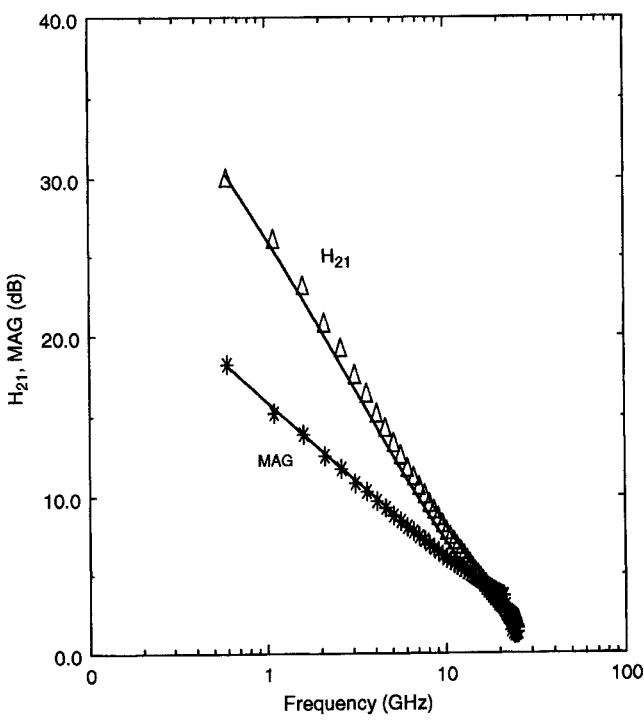

Fig. 12. Comparison of the modeled (solid lines) and measured (symbols) frequency response at  $V_{BE} = 1.5$  V and  $V_{CE} = 2.5$  V.

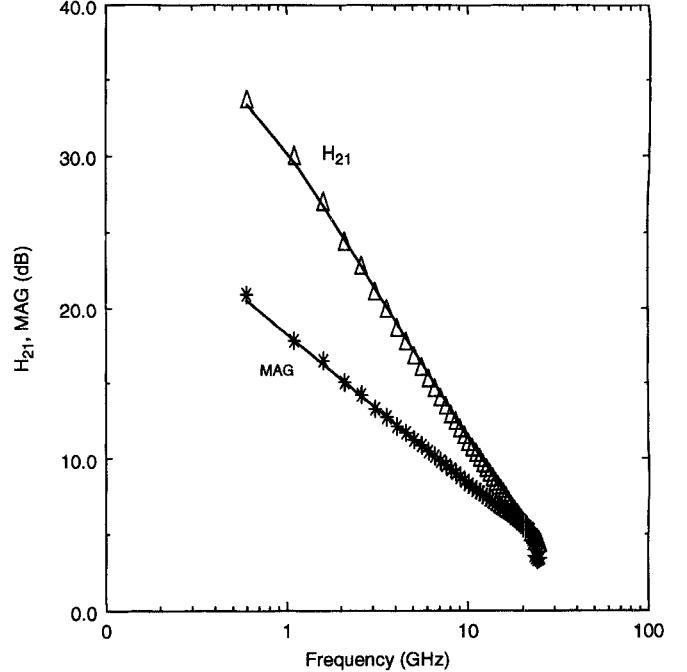

Fig. 11. Comparison of the modeled (solid lines) and measured (symbols) frequency response at  $V_{BE} = 1.6$  V and  $V_{CE} = 3.6$  V.

includes both surface and bulk recombinations is modeled by  $D_R$ , which has an ideality factor less than 2. The big difference between the ideality factors of the diodes makes it possible to extract the parameters of the diodes from different sections of  $I_B - V_{BE}$  curve.

The  $I_C - V_{BE}$  curve in the Gummel plot were used to extract the parameters of  $D_E$  and  $V_{EB}$ . As seen in Fig. 2, the

collector current has distinct  $V_{BE}$  dependences in different ranges of  $V_{BE}$ , indicating that the mechanism governing the current transport changes with  $V_{BE}$ . In the low range of  $V_{BE}$ , the diffusion process dominates. Thus the section of  $I_C - V_{BE}$  curve in that range is used to obtain the parameters of  $D_E$ . With increasing  $V_{BE}$  beyond a certain point, the ideality factor of  $I_C$  begins to change with the bias, which indicates the impact of the emitter barrier on collector current. It is noted that the variation of the ideality factor can not be attributed to emitter resistance since the effect of the resistance on  $I_C$  is negligible in this current range. Therefore, the parameters of the emitter barrier  $V_B$  can be determined from this section of  $I_C - V_{BE}$  curve, based on (10). As  $V_{BE}$  further increases, the effect of emitter resistance eventually becomes significant, and collector current is controlled by both emitter barrier and emitter resistance. The point at which the emitter resistance effect becomes important sets the upper boundary of the section of  $I_C - V_{BE}$  used to obtain the parameters of  $V_{EB}$ . Since the value of emitter resistance is pre-determined from the open-collector measurement, this point can be determined on  $I_C - V_{BE}$  curve.

#### C. Elements Related to Thermal Effects

The thermal-related elements in this model are  $R_{Th}$  for thermal resistance,  $V_{J,T}$  modeling the reduction of the emitter junction built-in potential and  $I_{PE,T}$  accounting for the increase in the reverse hole injection from emitter to base as the junction temperature rises. The thermal resistance can be obtained from the temperature dependence of  $V_{BE}$  via the power dissipation of the transistor  $P_{DISS}$

$$V_{BE}(T) = V_{BE}(T_0) + \frac{\Delta V_{BE}}{\Delta T} R_{Th} P_{DISS}. \quad (16)$$

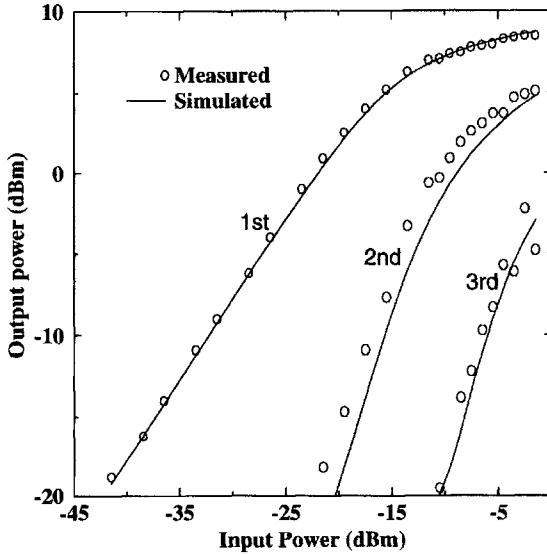

Fig. 13. Measured and simulated output power at fundamental frequency (2 GHz) and its harmonics versus input power at  $I_B = 0.1$  mA and  $V_{CE} = 3.0$  V.

Once the temperature coefficient  $\Delta V_{BE}/\Delta T$  is determined by measuring  $V_{BE}$  at different substrate temperatures,  $R_{Th}$  can be extracted from the slope of  $V_{BE} - P_{DISS}$  curve. The extracted value of  $R_{Th}$  was confirmed by liquid crystals measurements.

The parameters for  $V_{J,T}$  are extracted from the  $I$ - $V$  characteristics of  $E - B$  junction diode at different ambient temperatures and verified by the  $I_C - V_{CE}$  characteristics under constant  $V_{BE}$  conditions. The parameters for  $I_{PE,T}$  can be determined from the  $I_C - V_{CE}$  plot under constant  $I_B$  conditions where  $I_C$  decreases with  $V_{CE}$ . It should be noted that it is important to use  $I_C - V_{CE}$  plots under both constant  $I_B$  and  $V_{BE}$  conditions to construct the thermal model. Temperature effect parameters extracted only from the  $I_C - V_{CE}$  characteristics under constant  $I_B$  conditions, as was done in some HBT thermal models, may lead to an incorrect thermal-effect model. For example, all the thermal effects may be incorrectly attributed to the reduction in the base transport factor with temperature.

#### D. Parameters of Bias-Dependent Capacitors

Four capacitors are used to model the bias-dependent frequency/transient response of HBT's. The parameters in determining the emitter junction depletion capacitor  $C_E$  were obtained by fitting the measured  $E - B$  junction capacitance as a function of the applied voltage. The measured  $B - C$  junction capacitance data were used to extract the parameters for calculations of the extrinsic collector capacitance  $C_{CX}$  and the voltage-independent part (the  $C(V_D)$  in (13)) of the intrinsic capacitance  $C_{CI}$ . In this extraction, the same voltage dependence was assumed for both  $C_{CX}$  and  $C_{CI}$  and the measured total capacitance at zero bias was partitioned between  $C_{CX}$  and  $C_{CI}$  according to the area ratio of the intrinsic to the extrinsic collector. The parameters for the current-dependent part of  $C_{CI}$  [see (11)] are determined from the difference of the measured B-C junction capacitance ( $I_C = 0$ ) and the capacitance calculated from the small signal  $H_{21}$

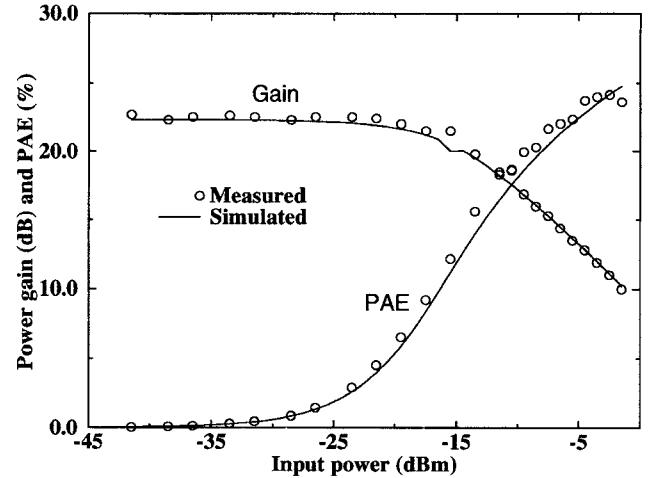

Fig. 14. Measured and simulated power gain and PAE versus input power under the condition of Fig. 13.

at various collector currents [9]

$$C_{CT} = - \left[ \omega \operatorname{Im} \left( \frac{I + H_{21}}{H_{22}} \right) \right]^{-1}. \quad (17)$$

In order to extract the parameters for the transit time capacitance  $C_{Tr}$ , the small signal HBT model was first optimized against the measured  $S$ -parameters at different biases. In the optimization, all the elements except  $C_{BE}$  (the total capacitance appeared at the  $E - B$  junction) were fixed at the values obtained with the techniques described before, i.e.,  $C_{BE}$  was the only variable to be determined by the optimization. With  $C_{BE}$  values obtained at different biases, the dependent of  $C_{BE}$  on  $V_{BC}$  and  $I_C$  was determined. This dependence, together with the known relationship between the junction depletion capacitance  $C_E$  and  $V_{BC}$  was used to deduce the parameters of  $C_{Tr}$ .

#### IV. MODEL VERIFICATION

To verify the model, it was applied to HBT's with various emitter sizes [10]. An example is given here for a composite HBT consisting of ten circular emitters with  $2.5 \mu\text{m}$  diameter. Figs. 3–5 show the dc characteristics calculated from the developed model and obtained from measurement. The emitter junction depletion capacitance and the total collector capacitance (at  $I_C = 0$ ) obtained from the model and from the junction diode measurement are compared in Figs. 6 and 7. To demonstrate the validity of the model for ac analysis over a wide range of operating biases and signal frequencies, the  $S$ -parameters,  $H_{21}$  and  $G_{\max}$  under five different bias conditions were calculated by using the model. The five operating points cover the major area of the  $I_C - V_{CE}$  characteristics in Fig. 5. Figs. 8–12 compare the results from the calculation with the measured data. To further verify the validation of the large-signal model, a power sweep measurement was performed for a common-emitter device biases under class A condition and with  $50 \Omega$  output termination. Figs. 13 and 14 show the measured and simulated output power at fundamental frequency of 2 GHz and at its harmonics, power gain, and power added efficiency PAE. The agreement between the

measured and the modeled data, as shown in these figures, is excellent.

## V. CONCLUSION

A new large-signal HBT model, implemented in SPICE, has been developed. With the inclusion of the effects important for HBT operations and the use of an accurate extraction procedure for the model parameters, an excellent agreement between the measured and the modeled data has been achieved over a wide range of operating biases and frequencies. Several new effects were identified from experimental observations during the development of the model. These findings contribute to better understanding HBT operations and to the design optimization of the devices and circuits.

## ACKNOWLEDGMENT

The authors would like to thank ITRC for its support.

## REFERENCES

- [1] H. K. Gummel *et al.*, "An integral charge control model of bipolar transistors," *Bell Syst. Tech. J.*, vol. 49, p. 827, 1970.

- [2] P. C. Grossman *et al.*, "Large signal modeling of HBT's including self-heating and transit time effects," *IEEE Trans. Microwave Theory Tech.*, vol. 40, 1992, p. 449.

- [3] P. Baureis *et al.*, "Modeling of self-heating in GaAs/AlGaAs HBT's for accurate circuit and device analysis," *GaAs Ic Symp.*, p. 125, 1991.

- [4] C. McAndrew, "A complete and consistent electrical/thermal HBT model," *IEEE Bipolar Circ. Tech. Meet.*, Oct. 1992, p. 200.

- [5] W. Liu *et al.*, "Current transport mechanism in GaInP/GaAs heterojunction bipolar transistors," *IEEE Trans. Electron Dev.*, vol. 40, 1993, p. 1378.

- [6] S. M. Sze, *Physics of Semiconductor Devices*, 2nd ed., p. 74, 1981.

- [7] E. Getreu, *Modeling the Bipolar Transistor*. Amsterdam, The Netherlands: Elsevier, 1978, p. 140.

- [8] D. E. Dawson *et al.*, "CW measurement of HBT thermal resistance," *IEEE Trans. Electron Dev.*, vol. 39, 1992, p. 2235.

- [9] D. R. Pehlke and D. Pavlidis, *IEEE Trans. Microwave Theory Tech.*, vol. 40, no. 12, Dec. 1992, pp. 2367-2373.

- [10] T. Lester *et al.*, "A manufacturable process for HBT circuits," *Proc. 20th Int. Sy. GaAs Related Compounds*, 1993.

**Q. M. Zhang**, photograph and biography not available at the time of publication.

**Huntao Hu** received the B.S.E.E. degree from The University of Electrical Science and Technology of China, Chengdu, Sichuan, People's Republic of China, in 1982, and the M.S.E. degree and the Ph.D degree in electrical engineering from the University of Michigan, Ann Arbor, in 1986 and 1991, respectively.

From 1982 to 1985, he worked on the research and fabrication of CMOS and CCD devices at the Sichuan Solid State Circuits Research Institute, Sichuan, China. In 1986, he joined the Center for

High Frequency Microelectronics and the Solid State Electronics Laboratory at the University of Michigan as a Research Assistance, where he worked on the development of the processing technology of *III - IV* compound semiconductor devices, and did the Monte Carlo simulation and design of heterojunction bipolar transistors for high speed/frequency applications. Since 1991, he has been with the Advanced Technology Laboratory of Bell-Northern Research (now Nortel Technology), Ottawa, Canada, being involved in the development of processing technology, performing computer simulation of devices, and currently working on the device modeling and characterization.

**John Sitch** was born in London and educated at Netteswell Comprehensive School, Harlow and Pembroke College Oxford, where he received the B.A. degree in engineering science. After working for two years as a development engineer at Plessey Radio Systems, he received the M.E. degree in microwave and communications engineering from the Universities of Leeds and Sheffield, Sheffield, and the Ph.D. degree in electronics from the University of Sheffield.

After completing his doctorate he was a Lecturer in electronics first at the University of Nottingham and then at the University of Sheffield. Since 1984 he has been with BNR's Advanced Technology Laboratory in Ottawa, where he is currently manager, Advanced High-Speed Projects, with interests including all aspects of *III-IV* IC's.

**R. K. Surridge**, photograph and biography not available at the time of publication.

**Jimmy M. Xu** received the Ph.D. degree in electrical engineering from the University of Minnesota, Minneapolis, in 1987.

He is a Professor of the Department of Electrical and Computer Engineering at the University of Toronto. He holds the title of James Ham Professor in Optoelectronics. He was awarded the 1995 Steacie Prize for contributions to fundamental and applied quantum electronics, and a 1995 Conference Board Canada-NSERC Award for "Best Practices in University-Industry R&D" (Honorable Mention). One of his students received the NSERC Doctoral Thesis Prize (Engineering), and another was given "The Best Student Paper Award LEOS'94." He is an Editor for the IEEE TRANSACTIONS ON ELECTRON DEVICES, and a co-editor for the 1996 Special Issue on Present and Future Trends in Device Science and Technology of the IEEE TRANSACTIONS ON ELECTRON DEVICES. He is a member of the IEEE Electron Device Society Meetings Committee, and ex-officio of the IEEE Electron Device Society Administration Committee. He is a Principal Investigator of the Ontario Laser and Lightwave Research Centre. He is also an investigator at the Ontario Centre for Material Research and a key associate of the Information Technology Research Centre. He has authored and coauthored over 90 referred papers in physics and engineering journals and over 50 referred conference papers. He has been granted eight patents on electronic and photonic devices. His current research interests include semiconductor physics, nanostructures, quantum electronics, and compound semiconductor device design, modeling, and measurements. Currently, he leads a group of researchers and graduate students of the Optoelectronics Laboratory at the University of Toronto and conducts research primarily in the areas of optoelectronics, quantum electronics, nanostructure physics, heterostructure transistors, quantum-well electronic and photonic devices well as large-scale computer simulations. The Optoelectronics Laboratory is sponsored by Nortel Technology, and conducts research projects funded by agencies and companies in Canada, USA, France, and Japan.